# Imaging Failures in Sub-Micron Devices and Measuring Stresses in 3D ICs

Andrew A. O. Tay, PhD (UNSW); Fellow, ASME; MIEEE. Senior Research Fellow (SUTD), Adjunct Prof (NUS)

# Imaging Failures in Sub-Micron Devices

#### Andrew A. O. Tay

Singapore University of Technology and Design

Dustin Kendig, Microsanj LLC, Santa Clara, USA

Ali Shakouri, Birck Nanotechnology Center, Purdue

University, West Lafayette, Indiana, USA

# **Today's Advanced Devices**

- Shrinking device features: 10s nm 100s um

- More complex circuit architectures

- 3-D Structures

- Higher power densities

- High speed response due to the small thermal mass

- Highly non-uniform

# Understanding Device Thermal Behavior

- More important now for ...

- Optimizing device performance and ensuring ...

- Long-term reliability

- Traditional\* thermal imaging techniques do not meet requirements:

- Require sub-micron spatial resolution ...

- Nanosecond time resolution and ...

- Good temperature resolution

<sup>\*</sup>IR Thermography, Liquid Crystal, Micro-Thermocouple, etc

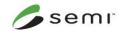

# Imaging Based on Thermoreflectance Principle

- Reflectance changes with material temperature

- Non-invasive thermal imaging technique exploits this ...

$$\frac{\Delta R}{R} = \left(\frac{1}{R} \frac{\partial R}{\partial T}\right) \Delta T = \kappa \Delta T.$$

*Thermoreflectance*

where κ is the *Thermoreflectance Coefficient*

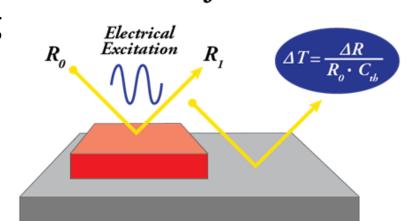

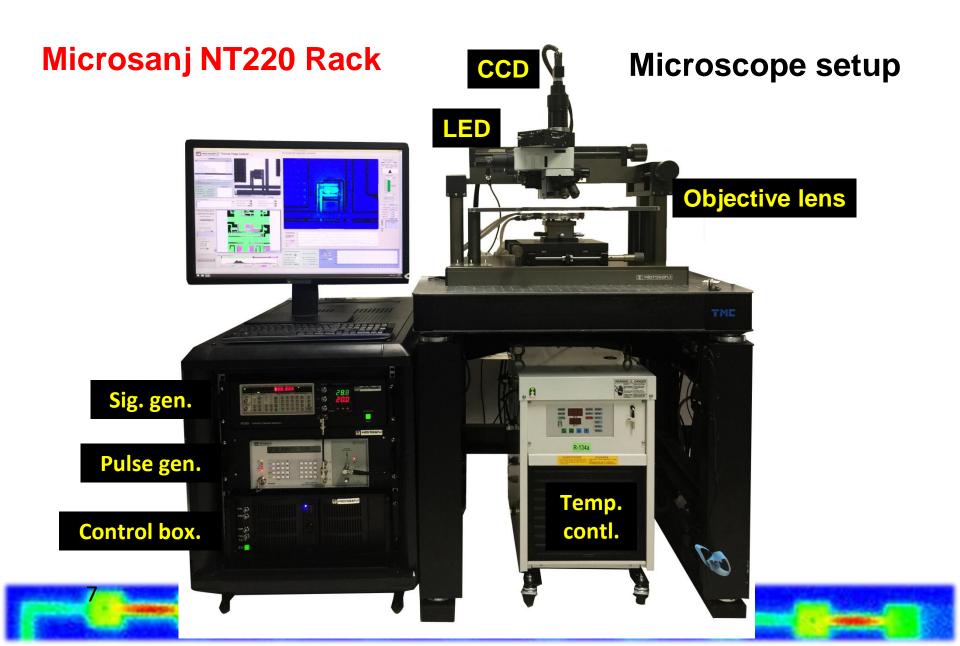

# **Basic Setup for Imaging**

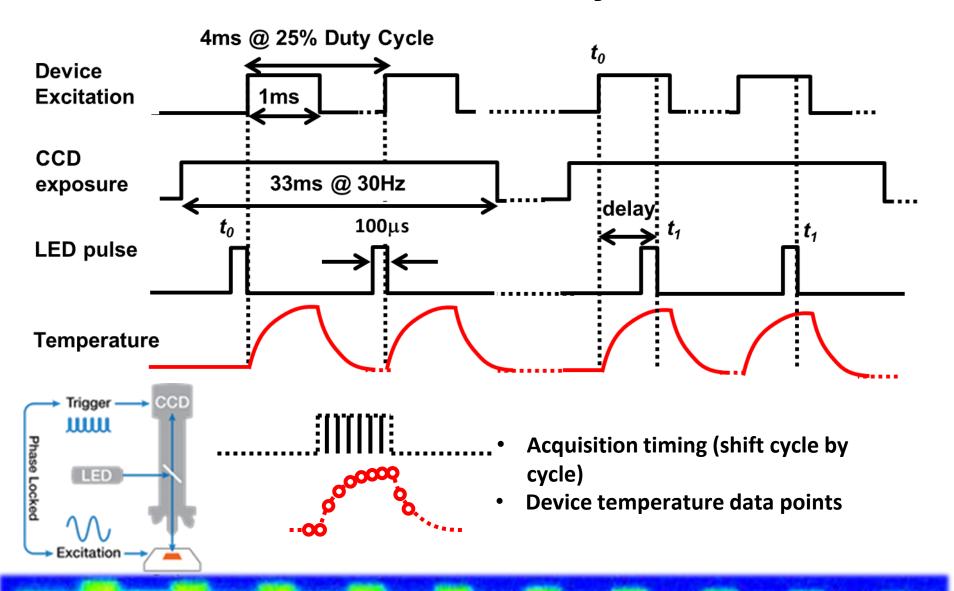

- LED illumination in visible range

- Lock-in technique to enhance

S/N ratio

- Thermoreflectance coefficient,

κ, is dependent on:

- Material

- LED wavelength

- Relatively independent of ambient temperature

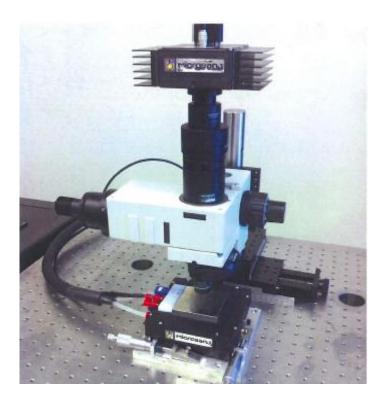

## **Thermoreflectance Imaging System**

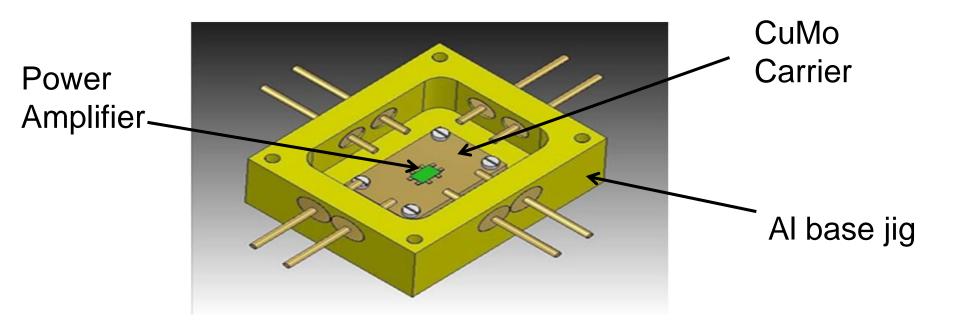

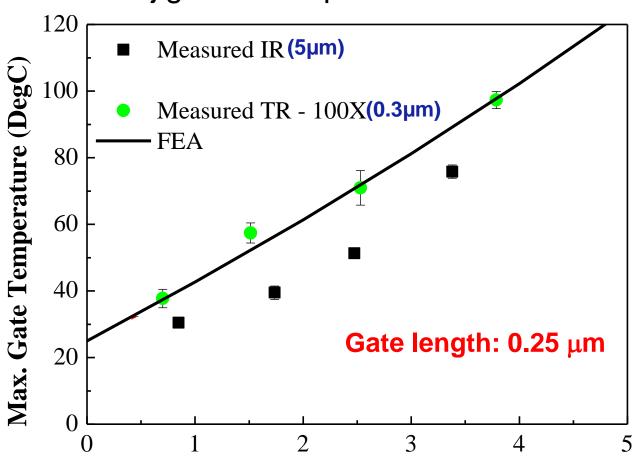

# Measurement of Gate Temperature of MMIC Device

- A GaN power amplifier MMIC device consisting of two gates.

- Length,  $L_g=0.25\mu m$ , Width,  $W_g=150\mu m$ , Pitch,  $P_g=48\mu m$

#### **Characterization Techniques**

#### Infrared (IRT)

#### Thermoreflectance (TTI)

### **Characteristics of Techniques**

#### Infrared (IRT)

- Based on blackbody radiation.

- Emissivity calibration over the surface

- Spatial resolution = 5µm.

#### Thermoreflectance (TTI)

- Based on change of reflectivity as a function of change in temperature.

- Characterization of material for thermoreflectance coefficient.

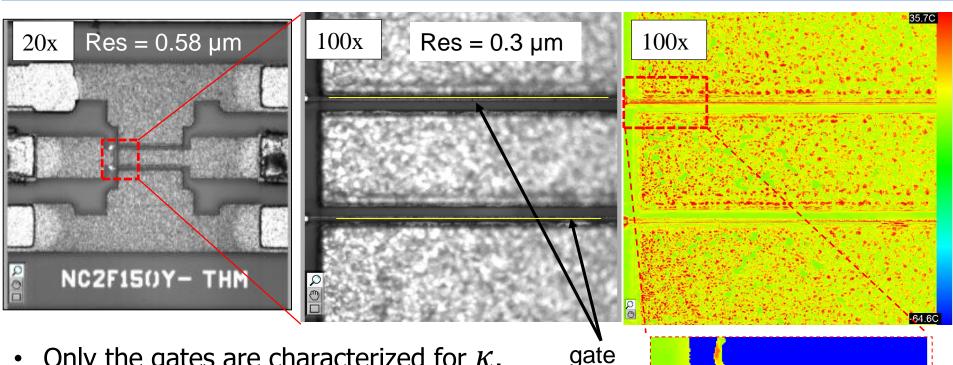

- Spatial resolution = 0.300μm (with 100x objective lens)

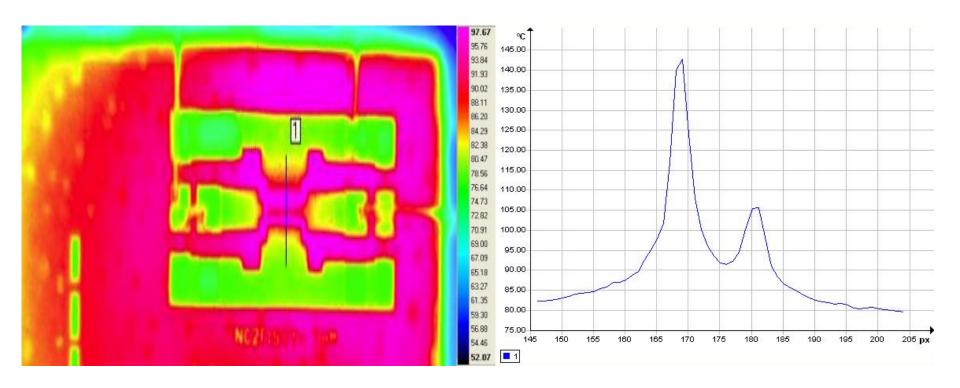

#### Thermoreflectance Temperature Measurement

- Only the gates are characterized for  $\kappa$ .

- Therefore, the temperature in regions around the gate is unknown.

- Temperatures around the gates (dark blue regions) are removed to show clearly the heating of the gates of length 0.25 um.

- The red color region indicated in the bottom picture corresponds to where the gate resides.

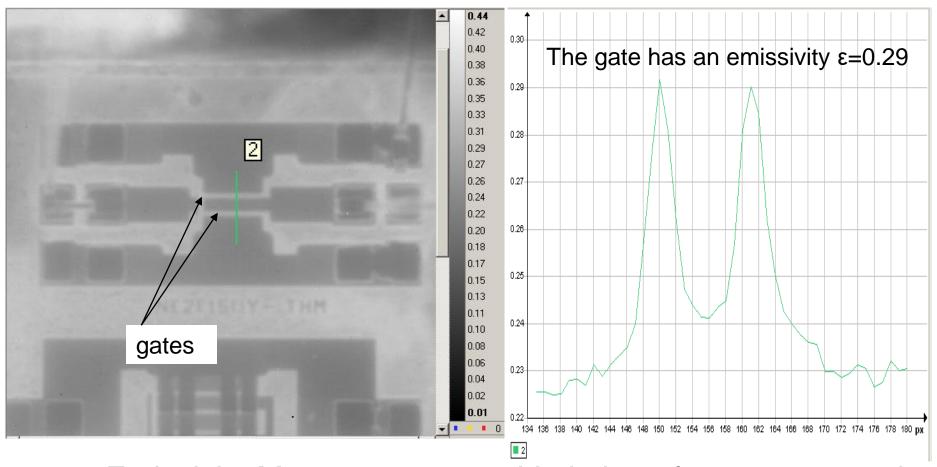

#### **Emissivity Correction for IRT**

**Emissivity Map**

Variation of ε along green line

## **Corrected IR Temperature Distribution**

#### Comparison of IRT, TTI and FEA

#### Aluminium jig base temperature of 25°C

Note importance of spatial resolution in accurate measurement of gate temperature.

P.A. Heat Dissipation (W/mm)

# Failure Analysis via Thermal Imaging

- Defects in devices often cause hot spots

- Transient thermal imaging can be used to detect hot spots and hence establish location of defects.

- Thermal behaviour of devices can also give clues to type of defects and failures.

## Transient Thermal Analysis of Logic IC

1.6mm

Area of interest: 20x zoom

1.1mm

500 μm thick Si

decapsulated, wire-bonded

# Heating history

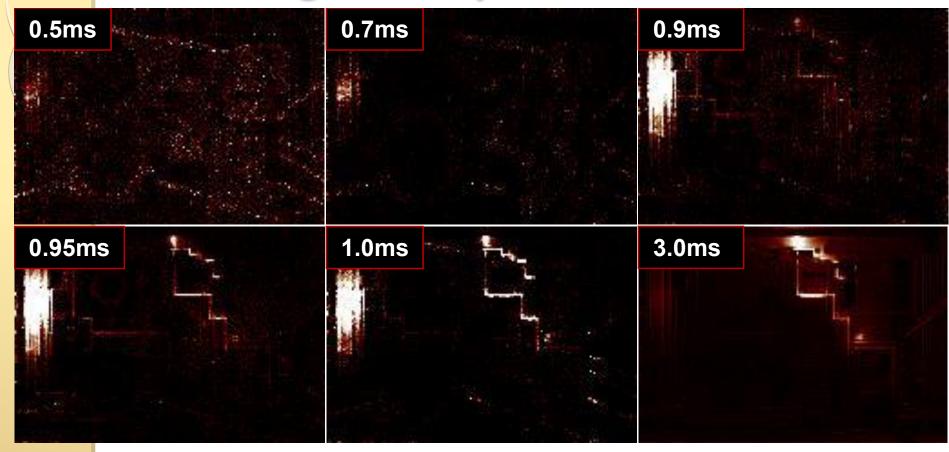

A series of thermal intensity contour maps versus elapsed time after applied bias. The brighter location indicates the higher temperature.

The temperature scale is common for all six images. Note that the right side top portion heats up quickly after approximately 1 ms.

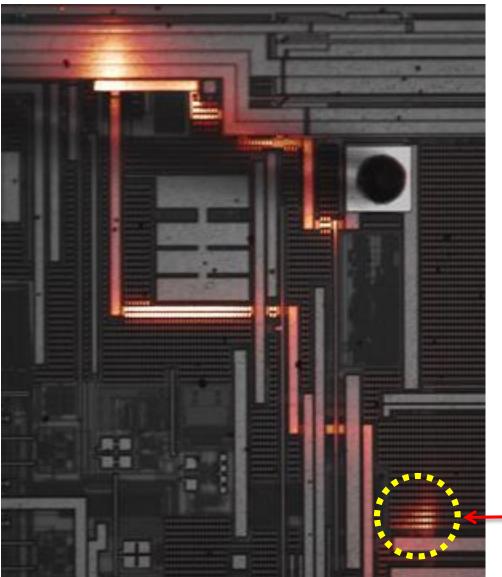

# Logic IC - local heat up

Logic sections located at the lower right undergo *latchup* where 250 mA of current flowed through V<sub>dd</sub> rather than the typical 10 mA.

This large current causes the power path to heat up → visible in the image.

Location of Latchup

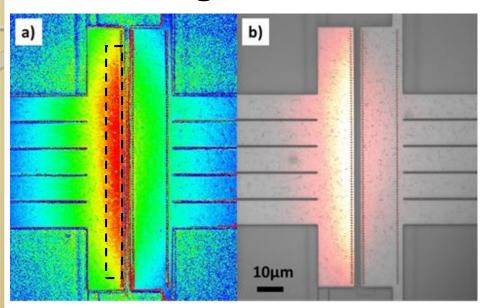

#### Thermal Characterization via TTI

- Thermal resistance,  $R_{th} = t/kA$  where t is the layer thickness, k is thermal conductivity, A is the area.

- TTI can be used to characterize k, if t is known.

- TTI can be used to measure *t*, if *k* is known. This can be used as a way of monitoring manufacturing quality in a non-destructive manner.

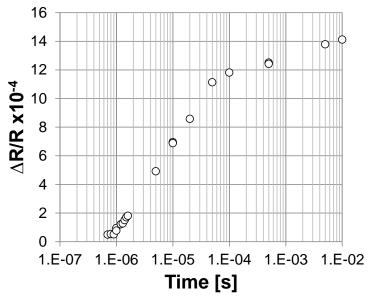

# Transient Analysis of a Power Diode

#### **Device image and thermal contour**

At 1 ms after step pulse started (715 mA).

Higher temperature in anode (left) due to accumulation of charged carriers. Mean temperature response at the marked location of the left contact (anode).

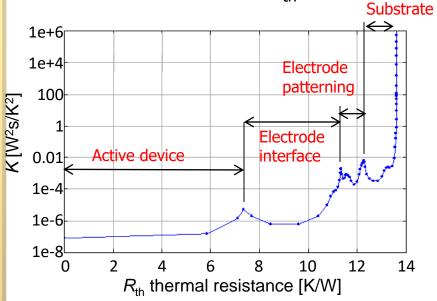

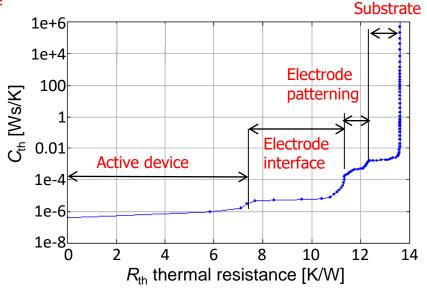

# Use Structure Functions to obtain $R_{th}$

Thermal network analysis by using the structure function method.

Differential structure function K vs Thermal resistance  $R_{th}$ .

Cumulative structure function  $C_{th}$  vs Thermal resistance  $R_{th}$ .

#### Conclusion

- Thermoreflectance thermal imaging (TTI) has high spatial resolution (< 300 nm), high temporal resolution (800 ps), high temperature resolution (0.1 °C).

- TTI is more accurate than IRT for imaging devices mainly due to >10X higher spatial resolution.

- TTI can be used for imaging and analyzing the rapid transient thermal behavior of devices including hot spots which indicate locations of device failure.

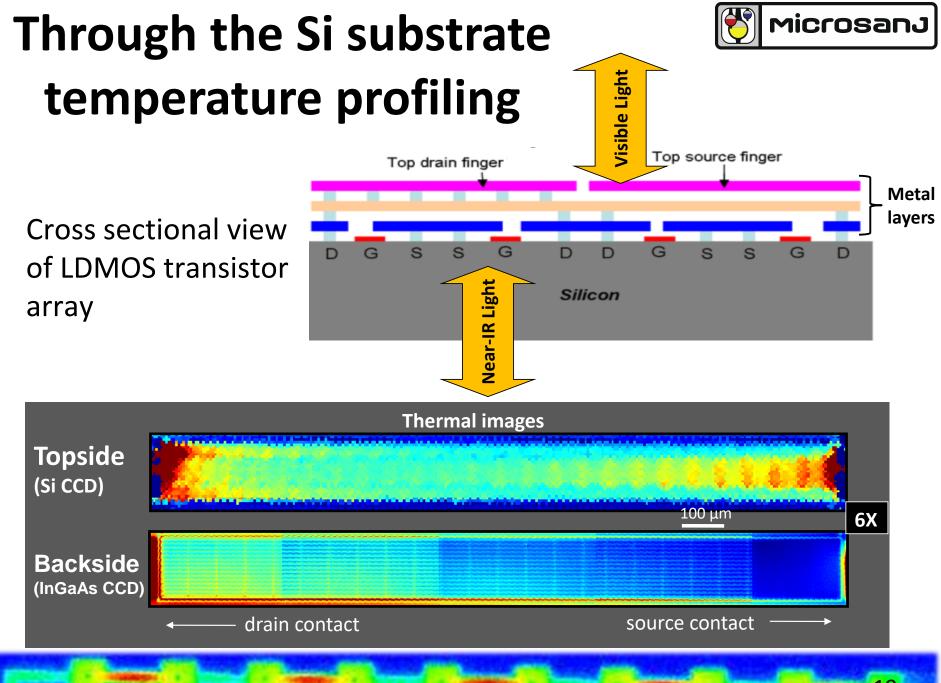

- TTI can be used to measure flip chip transistor temperatures by using NIR light through the Si substrate of flip chips.

- TTI meets the challenging requirements for thermal analysis of today's advanced devices.

# Measuring Stresses in TSVs of 3D IC Packages

Arief Budiman and Andrew A. O. Tay

Singapore University of Technology and Design

# Measurement of stresses in Cu and Si around through-silicon via (TSV) by synchrotron X-ray micro-diffraction for 3-dimensional integrated circuits

A.S. Budiman<sup>1,5</sup>, H.-A. Shin<sup>2</sup>, B.-J. Kim<sup>2</sup>, S.-H. Hwang<sup>2</sup>, H.-Y. Son<sup>3</sup>, M.-S. Suh<sup>3</sup>, Q.-H. Chung<sup>3</sup>, K.-Y. Byun<sup>3</sup>, N. Tamura<sup>4</sup>, M. Kunz<sup>4</sup>, Y.-C. Joo<sup>2</sup>

<sup>1</sup>Center for Integrated Nanotechnologies (CINT), Los Alamos National Laboratory (LANL), Los Alamos, NM 87545 <sup>2</sup>Dept. Of Materials Science & Engineering, Seoul National University (SNU), Republic of Korea <sup>3</sup>PKG Development Group, R&D Division, Hynix Semiconductor Inc., Republic of Korea <sup>4</sup>Advanced Light Source (ALS), Lawrence Berkeley National Laboratory (LBNL), Berkeley, CA 94720 <sup>5</sup>Singapore University of Technology and Design, Engineering Product Development, Singapore.

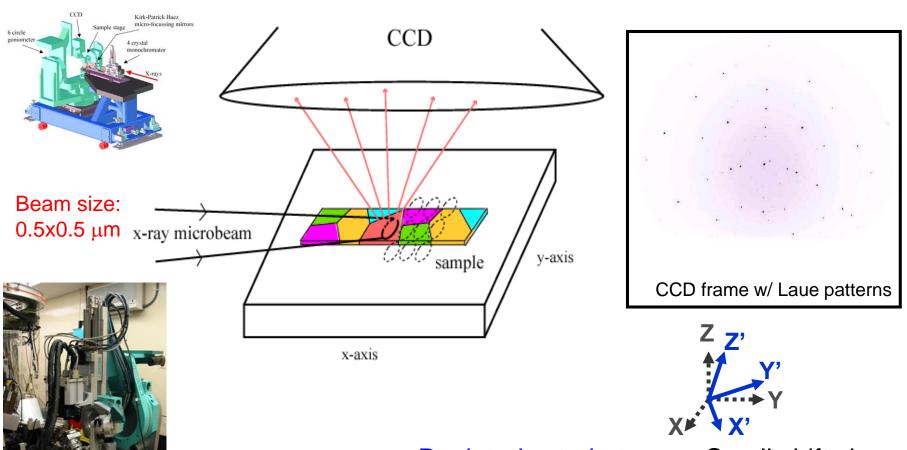

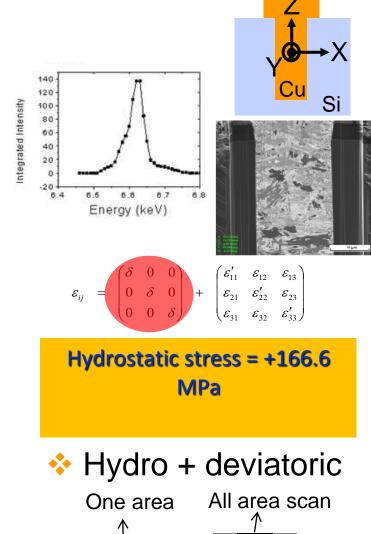

# Synchrotron X-Ray Submicron Diffraction

X-ray source: ALS Synchrotron, Berkeley Lab (Beamline 12.3.2)

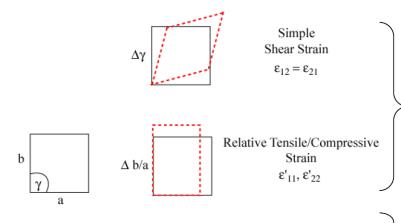

Deviatoric strain tensor: Small shifts in spot relative positions → Crystal deformation at constant volume (~ 10<sup>-4</sup> accuracy)

## Laue pattern and energy scanning

#### **Deviatoric Strains:**

Angles between atomic planes change, causing a shift in the positions of the Laue reflections

#### Laue pattern

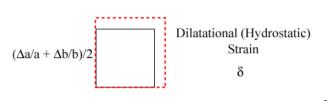

#### Dilatational Strain:

Volume of unit cell changes, Laue reflections do not shift positions, energy of the Laue reflection changes

#### **Energy scanning**

Total strain = dilatational + deviatoric (Energy scan) + (Laue pattern)

$$\varepsilon_{ij} = \begin{pmatrix} \delta & 0 & 0 \\ 0 & \delta & 0 \\ 0 & 0 & \delta \end{pmatrix} + \begin{pmatrix} \varepsilon'_{11} & \varepsilon_{12} & \varepsilon_{13} \\ \varepsilon_{21} & \varepsilon'_{22} & \varepsilon_{23} \\ \varepsilon_{31} & \varepsilon_{32} & \varepsilon'_{33} \end{pmatrix}$$

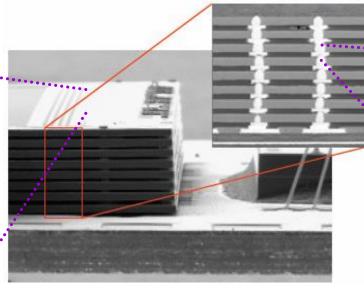

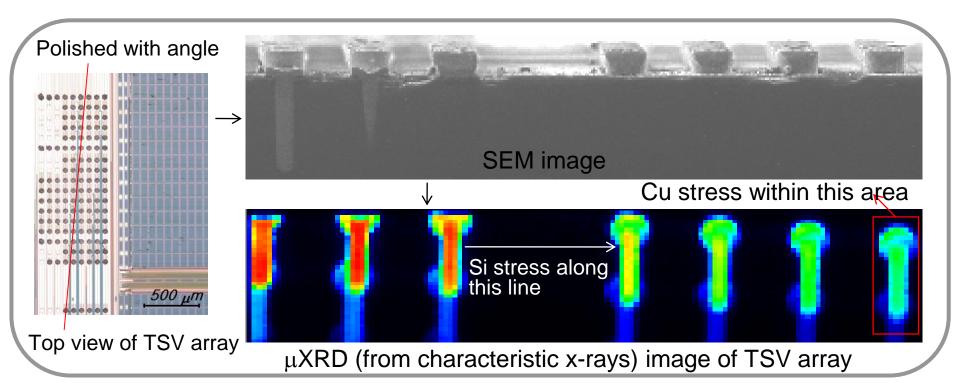

### Lab XRD vs Synchrotron µXRD

Laboratory XRD usually cannot be used for measuring stress in small TSVs as it has a resolution of about 70  $\mu$ m which is inadequate.

TSV dia. 20 µm

#### Diameter 70 µm.

The resolution of a Synchrotron  $\mu$ XRD is 0.5  $\mu$ m which is very adequate.

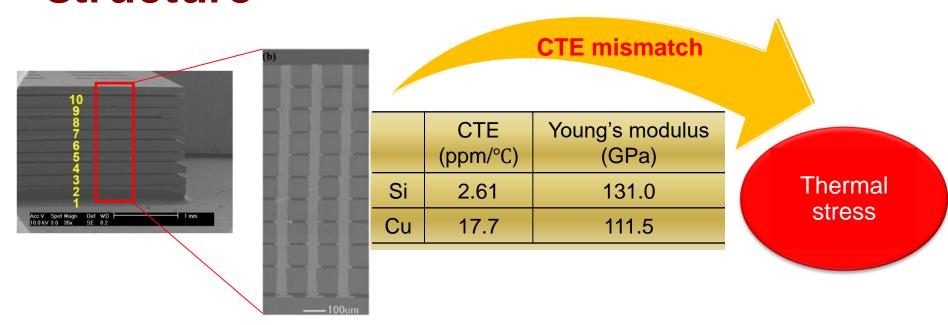

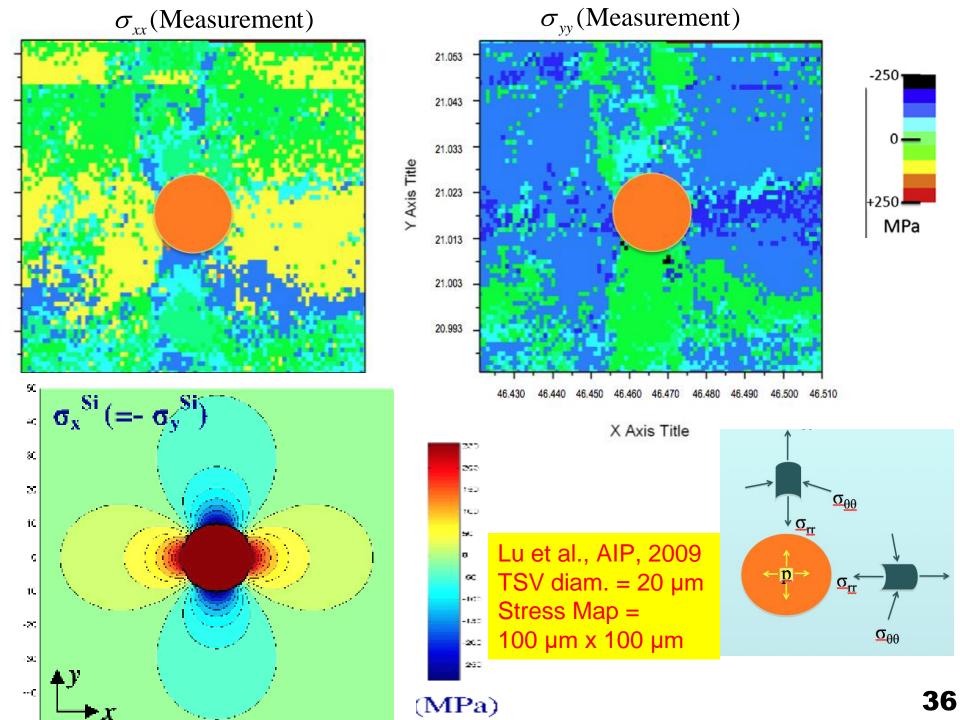

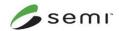

# Mechanical Stresses in TSV structure

- Cu TSV is embedded in Si matrix.

- Coefficient of thermal expansion (CTE) mismatch → thermal stress.

- Thermal stress can be induced during manufacturing or processing.

- Other origins of stress may include grain growth, chip-package interaction, wafer thinning, etc.

#### Impact on Reliability and Performance of Device

Si stress

Keep-away zone

Device must be kept away from the zone in which mobility is changed.

Si cracking

<Samsung Electronics>

Cu stress

Debonding, TSV cracking

TSV Pop-up, Bulging-up → Integration Issues

<Source: SEMATECH>

- Thermal stress of TSV → Si stress and Cu stress.

- Si stress (residual stress) → degradation of device performance.

- Cu stress (thermal stress) → mechanical failure of Cu TSV.

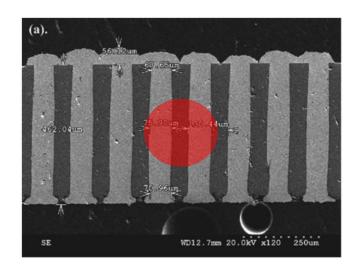

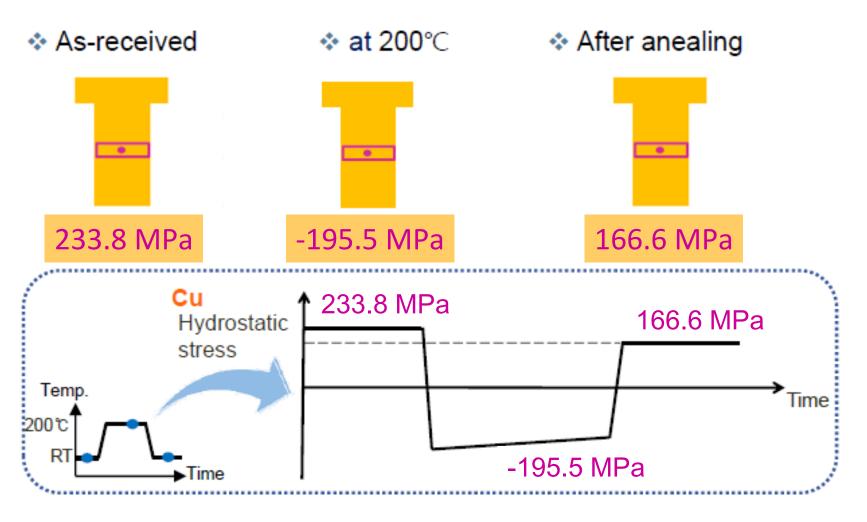

## Experimental – SK Hynix

- Sample

20 μm TSV diameter, 90 μm pitch, 90 μm height

- Condition of measurement

- Measurement of stress for : Si, Cu TSV

- Thermal treatment : in situ at 200 °C,

ex situ for post-annealed sample (200 °C for 1 hour)

Temp.

RT

200°C

Measurement

Time

Hydrostatic stress = -195.5 MPa

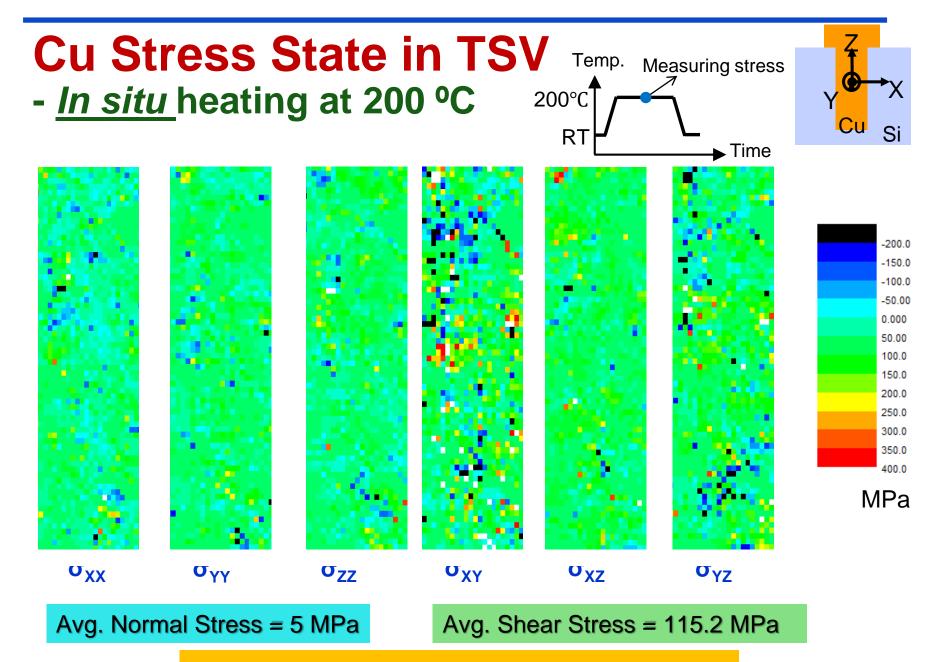

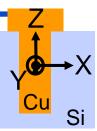

## Cu Stress State in TSV – SK Hynix

- Post Annealed Sample (measure at RT)

Only <u>deviatoric</u> components of stress  $\varepsilon_{ij} = 1$

#### Cu Hydrostatic Stress State in TSV – SK Hynix

- Post Annealed Sample (measure at RT)

## Stress Evolution in Cu TSV – SK Hynix

#### Cu hydrostatic stress

## Si Strain Profile from Edge of TSV

- Post Annealed Sample (measure at RT)

Si Keep-Away Zone of about 17 µm from Edge of TSV

# Summary

- Synchrotron X-ray submicron diffraction (white + monochromatic beam) has proven to be a powerful tool to measure stress states in TSV <u>in situ</u> and while the Cu via is still <u>buried inside the Silicon</u>

- <u>Cu stress state</u> is mostly tensile at the post-annealed state:

- Comparison SK Hynix vs. SEMATECH samples → RT grain growth leads to high tensile stress in the as-received state

- How to reduce stress-induced reliability/integration → reduce Cu hydro stress in the as-received state

- <u>Stress in Si surrounding Cu TSV</u> was found to follow Cu hydrostatic stress: higher Cu hydrostatic stress → higher Si stress → larger "keep-away zone"

- Si stress in array of TSV's → important for design/layout

- Stress scanning from the top would be valuable → to optimize layout!

# Acknowledgements

Sincere Thanks to - for Funding, Collaborations and Experimental Support

NATIONAL

RESEARCH

**FOUNDATION**

PRIME MINISTER'S OFFICE SINGAPORE

Energy Innovation Research Program (EIRP)

# Q & A

**Andrew Tay**

Email: andrew\_tay@ieee.org

# **Transient Thermal Analysis**